8 To 1 Multiplexer Verilog

A multiplexer is a device that selects one of several input signals and forwards the selected input to the output. Typical multiplexers come in 2:1, 4:1, 8:1, and 16:1 forms. A multiplexer of 2n inputs has n select lines. A TTL series 8:1 MUX is 74151. It has three select lines S2, S1, S0. Each of the 8. How can I construct an 8 x 1 multiplexer from two 4 x 1 multiplexers with enable inputs? Multiplexer Timing. Making 16x1 multiplexer by using two 8x1 multiplexer and one 2x1. Multiplexer circuit. Can we derive all boolean functions using a 2x1 Multiplexer? Design and develop the Verilog /VHDL code for an 8:1 multiplexer. Simulate and verify its working.

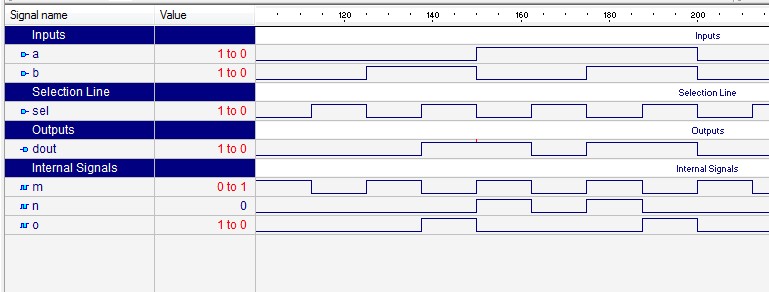

I need create 8*1 multiplexer by 2-1 multiplexer.At this time, my code can work. However, the output is incorrect.And the wires O_0.O_1,O_2,O_3 can work correctly.When the 2-1 multiplexer read the selector [1] and [2], it does not change.The output is between I0 AND I1.Can you help me with the problem? Or just tell me where the mistake is?

This is not italic `

This is not italic

Next, choose Visual Basic from the Language list, and then choose Windows from the Platform list.After you apply the language and platform filters, choose the Console App (.NET Core) template, and then choose Next.Then, in the Configure your new project window, type or enter WhatIsYourName in the Project name box.

- I'm new to verilog. I'm trying to implement a 2:1 multiplexer on a FPGA development board (DE1-SOC altera) using built in switches and LEDs. The following are the assignments that I'm using for.

- 8 to 1 Multiplexer HDL Verilog Code. This page of verilog sourcecode covers HDL code for 8 to 1 Multiplexer using verilog. Following is the symbol and truth table of 8 to 1 Multiplexer.

2 Answers

I believe, assign statement in the MUX_2_1 is not proper.

You have 2 options to rectify it.

1st Option

You can use ternary operator (which is more preferable, as per my opinion)

2nd OptionDatacard cp40 plus driver windows xp.

It seems that, you wrote this code, by considering the actual gate level schematic or netlist of the 2*1 mux.

But to mimic, the actual gate level design, you should consider ANDing of the individual bits of the i0, i1 nets.

So your code may look like this :

8 To 1 Mux Verilog

Now, you may wonder that, you need to copy same statement 32 times!!!!.

So you have an alternative for this :